EDA实验(Switches, Lights, and Multiplexers与Numbers and Displays与Latches, Flip-flops, and Registers)

日期: 2020-11-27 分类: 跨站数据测试 511次阅读

EDA实验

某高校学生,作为一名软件系的学生,秉着“层次化,模块化,自顶向下的设计,自底向上的实现”的理念学习EDA,学习一门硬件语言VHDL。在学习EDA的过程中,也深知学习EDA的烦恼。因此,本文将本人小白学习EDA的实验记录在此:

使用工具:Quartus II 9.1 软件 与 ALTERA DE2板

目录

- 实验一:Switches, Lights, and Multiplexers

- 实验二:Numbers and Displays

- 实验三:Latches, Flip-flops, and Registers

实验一:Switches, Lights, and Multiplexers

任务:实验一主要是实现“HELLO“的显示,并能通过外部控制移动“HELLO”。

介绍:外部输入SW[17…0]信号,其中SW[17…15]用于控制移动,SW[14…0]用于控制显示,通过八个不同的八选一数据选择器,将结果输出到8个数码显示器上。

VHDL代码:

--Part6.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY mux_3bit_5to1 IS

PORT (

n : IN INTEGER RANGE 0 TO 7;

S, U, V, W, X, Y : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

M : OUT STD_LOGIC_VECTOR(2 DOWNTO 0)

);

END mux_3bit_5to1;

ARCHITECTURE Behavior OF mux_3bit_5to1 IS

begin

process(n, S, U, V, W, X, Y ) is

begin

CASE n IS

WHEN 0 =>

CASE S IS

WHEN "011" => M <= U;

WHEN "100" => M <= V;

WHEN "101" => M <= W;

WHEN "110" => M <= W;

WHEN "111" => M <= X;

WHEN OTHERS => M <= Y;

END CASE;

WHEN 1 =>

CASE S IS

WHEN "010" => M <= U;

WHEN "011" => M <= V;

WHEN "100" => M <= W;

WHEN "101" => M <= W;

WHEN "110" => M <= X;

WHEN OTHERS => M <= Y;

END CASE;

WHEN 2 =>

CASE S IS

WHEN "001" => M <= U;

WHEN "010" => M <= V;

WHEN "011" => M <= W;

WHEN "100" => M <= W;

WHEN "101" => M <= X;

WHEN OTHERS => M <= Y;

END CASE;

WHEN 3 =>

CASE S IS

WHEN "000" => M <= U;

WHEN "001" => M <= V;

WHEN "010" => M <= W;

WHEN "011" => M <= W;

WHEN "100" => M <= X;

WHEN OTHERS => M <= Y;

END CASE;

WHEN 4 =>

CASE S IS

WHEN "111" => M <= U;

WHEN "000" => M <= V;

WHEN "001" => M <= W;

WHEN "010" => M <= W;

WHEN "011" => M <= X;

WHEN OTHERS => M <= Y;

END CASE;

WHEN 5 =>

CASE S IS

WHEN "110" => M <= U;

WHEN "111" => M <= V;

WHEN "000" => M <= W;

WHEN "001" => M <= W;

WHEN "010" => M <= X;

WHEN OTHERS => M <= Y;

END CASE;

WHEN 6 =>

CASE S IS

WHEN "101" => M <= U;

WHEN "110" => M <= V;

WHEN "111" => M <= W;

WHEN "000" => M <= W;

WHEN "001" => M <= X;

WHEN OTHERS => M <= Y;

END CASE;

WHEN 7 =>

CASE S IS

WHEN "100" => M <= U;

WHEN "101" => M <= V;

WHEN "110" => M <= W;

WHEN "111" => M <= W;

WHEN "000" => M <= X;

WHEN OTHERS => M <= Y;

END CASE;

END CASE;

end process;

END Behavior;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY char_7seg IS

PORT (

C : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

Display : OUT STD_LOGIC_VECTOR(0 TO 6)

);

END char_7seg;

ARCHITECTURE Behavior OF char_7seg IS

begin

process(C) is

begin

case C is

when "000" => Display <= "1001000"; --H

when "001" => Display <= "0110000"; --E

when "010" => Display <= "1110001"; --L

when "011" => Display <= "0000001"; --O

when others => Display <= "1111111"; --null

end case;

end process;

END Behavior;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY Part6 IS

PORT (

SW : IN STD_LOGIC_VECTOR(17 DOWNTO 0);

HEX0 : OUT STD_LOGIC_VECTOR(0 TO 6);

HEX1 : OUT STD_LOGIC_VECTOR(0 TO 6);

HEX2 : OUT STD_LOGIC_VECTOR(0 TO 6);

HEX3 : OUT STD_LOGIC_VECTOR(0 TO 6);

HEX4 : OUT STD_LOGIC_VECTOR(0 TO 6);

HEX5 : OUT STD_LOGIC_VECTOR(0 TO 6);

HEX6 : OUT STD_LOGIC_VECTOR(0 TO 6);

HEX7 : OUT STD_LOGIC_VECTOR(0 TO 6)

);

END Part6;

ARCHITECTURE Behavior OF part6 IS

COMPONENT mux_3bit_5to1

PORT (

n : IN INTEGER RANGE 0 TO 7;

S, U,V, W, X,Y : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

M : OUT STD_LOGIC_VECTOR(2 DOWNTO 0)

);

END COMPONENT;

COMPONENT char_7seg

PORT (

C : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

Display : OUT STD_LOGIC_VECTOR(0 TO 6)

);

END COMPONENT;

SIGNAL M0, M1, M2, M3, M4, M5, M6, M7 : STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

M_0: mux_3bit_5to1 PORT MAP (0, SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9),

SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M0);

H0: char_7seg PORT MAP (M0, HEX7);

M_1: mux_3bit_5to1 PORT MAP (1, SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9),

SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M1);

H1: char_7seg PORT MAP (M1, HEX6);

M_2: mux_3bit_5to1 PORT MAP (2, SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9),

SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M2);

H2: char_7seg PORT MAP (M2, HEX5);

M_3: mux_3bit_5to1 PORT MAP (3, SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9),

SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M3);

H3: char_7seg PORT MAP (M3, HEX4);

M_4: mux_3bit_5to1 PORT MAP (4, SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9),

SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M4);

H4: char_7seg PORT MAP (M4, HEX3);

M_5: mux_3bit_5to1 PORT MAP (5, SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9),

SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M5);

H5: char_7seg PORT MAP (M5, HEX2);

M_6: mux_3bit_5to1 PORT MAP (6, SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9),

SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M6);

H6: char_7seg PORT MAP (M6, HEX1);

M_7: mux_3bit_5to1 PORT MAP (7, SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9),

SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M7);

H7: char_7seg PORT MAP (M7, HEX0);

END Behavior;

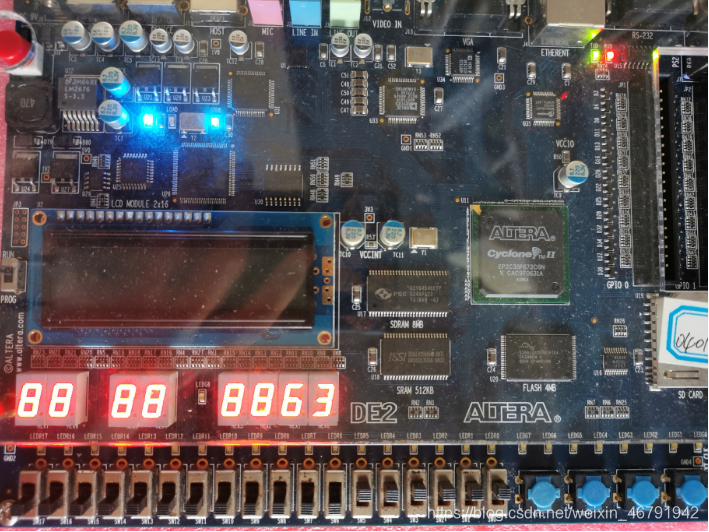

成果图:

实验二:Numbers and Displays

任务:实验二主要是将六位二进制数转换成两位十进制数,并显示在数码管上。

介绍:外部输入SW[5…0]信号,代表六位二进制数,输入两位十进制数,显示在最后两个数码显示器上。(六位二进制数最大代表两位十进制数63)

VHDL代码:

--Part7.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY b6_bit_to2_BCD IS

PORT (

Input : IN STD_LOGIC_VECTOR(5 DOWNTO 0);

OT, OU : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END b6_bit_to2_BCD;

ARCHITECTURE Behavior OF b6_bit_to2_BCD IS

SIGNAL T :STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL D, R : STD_LOGIC_VECTOR(5 DOWNTO 0);

begin

PROCESS (Input)

begin

T <= "0000";

D <= "000000";

if Input(5 DOWNTO 4) = "00" then

if Input(3 DOWNTO 0) > "1001" then

T <= "0001";

D <= "001010";

end if;

elsif Input(5 DOWNTO 4) = "01" then

if Input(3 DOWNTO 0) < "0100" then

T <= "0001";

D <= "001010";

elsif Input(3 DOWNTO 0) < "1110" then

T <= "0010";

D <= "010100";

else

T <= "0011";

D <= "011110";

end if;

elsif Input(5 DOWNTO 4) = "10" then

if Input(3 DOWNTO 0) < "1000" then

T <= "0011";

D <= "011110";

else

T <= "0100";

D <= "101000";

end if;

else

if Input(3 DOWNTO 0) < "0010" then

T <= "0100";

D <= "101000";

elsif Input(3 DOWNTO 0) < "1100" then

T <= "0101";

D <= "110010";

else

T <= "0110";

D <= "111100";

end if;

end if;

END PROCESS;

R <= Input(5 DOWNTO 0) - D;

OT <= T;

OU <= R(3 DOWNTO 0);

end Behavior;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY char_7seg IS

PORT (

C : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Display : OUT STD_LOGIC_VECTOR(0 TO 6)

);

END char_7seg;

ARCHITECTURE Behavior OF char_7seg IS

begin

process(C) IS

begin

CASE C IS

WHEN "0000" => Display <= "1000000"; --0

WHEN "0001" => Display <= "1111001"; --1

WHEN "0010" => Display <= "0100100"; --2

WHEN "0011" => Display <= "0110000"; --3

WHEN "0100" => Display <= "0011001"; --4

WHEN "0101" => Display <= "0010010"; --5

WHEN "0110" => Display <= "0000010"; --6

WHEN "0111" => Display <= "1111000"; --7

WHEN "1000" => Display <= "0000000"; --8

WHEN "1001" => Display <= "0010000"; --9

WHEN others => Display <= "1111111"; --null

END CASE;

end process;

END Behavior;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

entity Part7 is

port

(

SW : in STD_LOGIC_VECTOR(17 DOWNTO 0);

HEX1, HEX0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

end Part7;

architecture fun of Part7 is

COMPONENT b6_bit_to2_BCD

PORT (

Input : IN STD_LOGIC_VECTOR(5 DOWNTO 0);

OT, OU: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END COMPONENT;

COMPONENT char_7seg

PORT (

C : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Display : OUT STD_LOGIC_VECTOR(0 TO 6)

);

END COMPONENT;

SIGNAL OT, OU : STD_LOGIC_VECTOR(3 DOWNTO 0);

begin

tra: b6_bit_to2_BCD PORT MAP (SW(5 DOWNTO 0), OT, OU);

H1: char_7seg PORT MAP (OT, HEX1);

H0: char_7seg PORT MAP (OU, HEX0);

end fun;

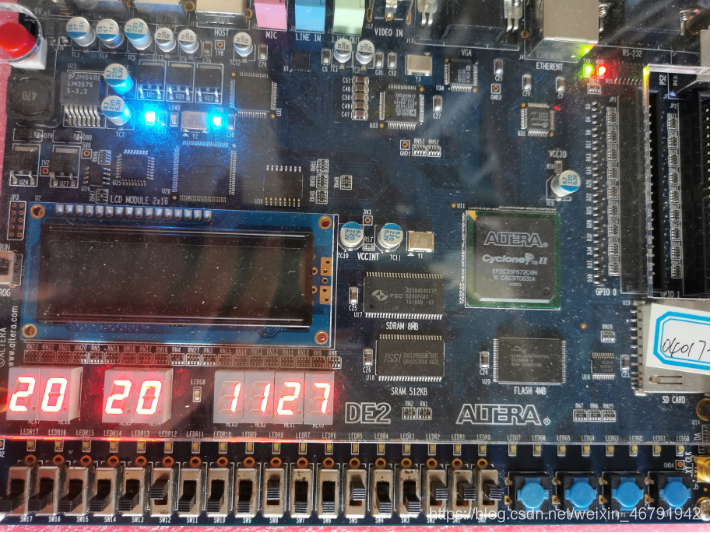

成果图:

实验三:Latches, Flip-flops, and Registers

任务:实验三主要是实现利用锁存器实现开关的重复利用。

介绍:外部输入SW[17…0]、KEY[1]、KEY[0],其中SW[17…0]用于显示,KEY[1]用于锁存器的脉冲端,KEY[0]用于锁存器的异步置零端。一开始输入的SW[17…0]信号显示在HEX3-HEX0的数码显示器上,通过KEY[1],可将当前SW[17…0]信号显示到HEX7-HEX4上。接着再次外部输入SW[17…0]信号显示在HEX3-HEX0的数码显示器上。这样就实现了开关的复用。通过KEY[0],可将HEX7-HEX4的显示置零。

VHDL代码:

--Part5.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY latch_rise IS

PORT (

D : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

CLK1, CLK2 : IN STD_LOGIC;

Q : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)

);

END latch_rise;

ARCHITECTURE Behavior OF latch_rise IS

BEGIN

PROCESS (D, CLK1)

BEGIN

IF CLK2 = '0' THEN

Q <= "0000000000000000";

ELSIF (CLK1'EVENT and CLK1 = '1') THEN

Q <= D;

END IF;

END PROCESS;

END Behavior;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY char_7seg IS

PORT (

C : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Display : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END char_7seg;

ARCHITECTURE Behavior OF char_7seg IS

--SIGNAL Cm : STD_LOGIC_VECTOR(3 DOWNTO 0);

begin

process(C)

begin

CASE C IS

WHEN "0000" => Display <= "0000001"; --0

WHEN "0001" => Display <= "1001111"; --1

WHEN "0010" => Display <= "0010010"; --2

WHEN "0011" => Display <= "0000110"; --3

WHEN "0100" => Display <= "1001100"; --4

WHEN "0101" => Display <= "0100100"; --5

WHEN "0110" => Display <= "0100000"; --6

WHEN "0111" => Display <= "0001111"; --7

WHEN "1000" => Display <= "0000000"; --8

WHEN "1001" => Display <= "0000100"; --9

WHEN "1010" => Display <= "0001000"; --a

WHEN "1011" => Display <= "1100000"; --b

WHEN "1100" => Display <= "0110001"; --c

WHEN "1101" => Display <= "1000010"; --d

WHEN "1110" => Display <= "0110000"; --e

WHEN "1111" => Display <= "0111000"; --f

END CASE;

end process;

END Behavior;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY part5 IS

PORT (

SW : IN STD_LOGIC_VECTOR(17 DOWNTO 0);

KEY : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

HEX7, HEX6, HEX5, HEX4 : OUT STD_LOGIC_VECTOR(0 TO 6);

HEX3, HEX2, HEX1, HEX0 : OUT STD_LOGIC_VECTOR(0 TO 6)

);

END part5;

ARCHITECTURE Structural OF part5 IS

COMPONENT latch_rise

PORT (

D : IN STD_LOGIC_VECTOR(15 DOWNTO 0);

CLK1, CLK2 : IN STD_LOGIC;

Q : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)

);

END COMPONENT;

COMPONENT char_7seg

PORT (

C : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Display : OUT STD_LOGIC_VECTOR(0 TO 6)

);

END COMPONENT;

SIGNAL Qa : STD_LOGIC_VECTOR(15 DOWNTO 0);

begin

D1: latch_rise PORT MAP (SW(15 DOWNTO 0), KEY(1), KEY(0), Qa);

H7: char_7seg PORT MAP (Qa(15 DOWNTO 12), HEX7);

H6: char_7seg PORT MAP (Qa(11 DOWNTO 8), HEX6);

H5: char_7seg PORT MAP (Qa(7 DOWNTO 4), HEX5);

H4: char_7seg PORT MAP (Qa(3 DOWNTO 0), HEX4);

H3: char_7seg PORT MAP (SW(15 DOWNTO 12), HEX3);

H2: char_7seg PORT MAP (SW(11 DOWNTO 8), HEX2);

H1: char_7seg PORT MAP (SW(7 DOWNTO 4), HEX1);

H0: char_7seg PORT MAP (SW(3 DOWNTO 0), HEX0);

end Structural;

成果图:

以上就是这次EDA课程中的实验。在此记录下学习的过程。

除特别声明,本站所有文章均为原创,如需转载请以超级链接形式注明出处:SmartCat's Blog

标签:vhdl 笔记 vhdl

上一篇: XCTF 攻防世界 Web题的基本知识点

下一篇: Go如何关闭exec可执行程序

精华推荐